Project Details

Performance Improvement of 16-bit RISC Processor Using Vedic Multiplier and High Speed Adders

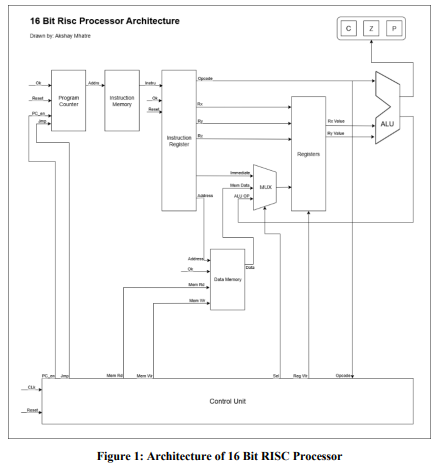

This project presents the design and performance enhancement of a 16-bit RISC processor through the integration of a Vedic multiplier. The objective is to improve the processor’s computational efficiency, reduce latency, and optimize hardware resource utilization by replacing the conventional shift-and-add multiplication unit with a Vedic multiplication architecture. The Vedic multiplier, based on ancient Indian mathematical principles, is known for its parallelism and speed, making it well-suited for high-performance embedded applications.

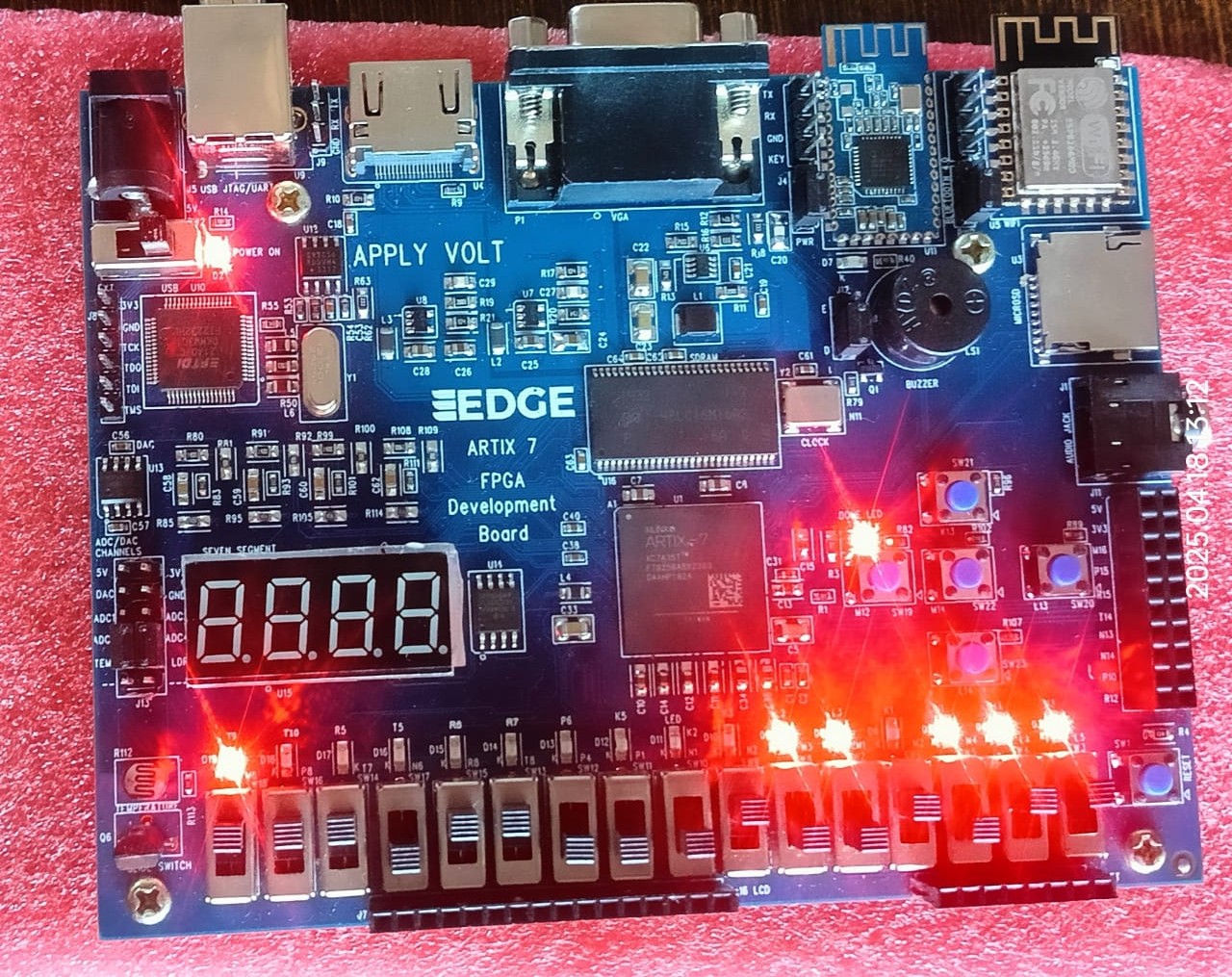

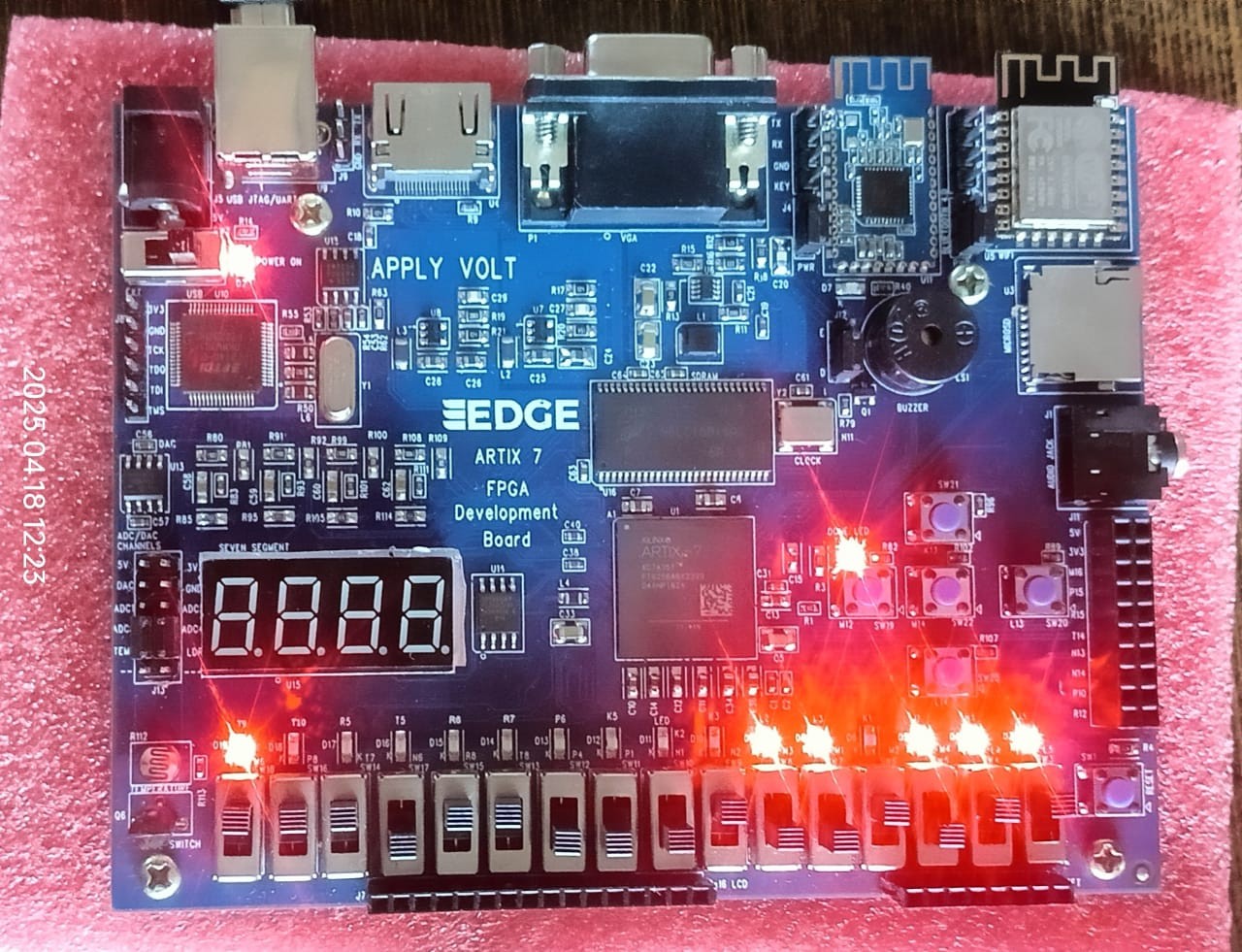

The processor was designed using Verilog HDL and implemented using the Xilinx Vivado Design Suite, targeting two FPGA platforms: Artix-7 (XC7A35TFTG256-1) and Spartan-7 (XC7S15FTGB196-1). Post-synthesis and implementation reports were analyzed to compare the performance, area, and power metrics of the processor before and after the integration of the Vedic multiplier. The results demonstrate notable improvements in processing speed and efficiency, validating the practical benefits of incorporating Vedic arithmetic in modern processor architectures.

The primary objective of this project is to significantly improve the performance of a 16-bit RISC processor by incorporating advanced arithmetic techniques such as Vedic multipliers and high-speed adder architectures. By leveraging the efficiency of Vedic mathematics for multiplication and optimizing addition operations through high-speed adder designs, the project aims to reduce computation time, minimize hardware delay, and enhance the overall throughput of the processor. This approach not only accelerates arithmetic operations but also contributes to lower power consumption and efficient resource utilization, making the processor suitable for high-performance embedded systems, real-time applications, and modern digital signal processing tasks. The project ultimately demonstrates a practical methodology to optimize processor design and achieve faster, more reliable computational performance.

- Simulated and tested the processor with various instruction sets to verify functionality and accuracy.

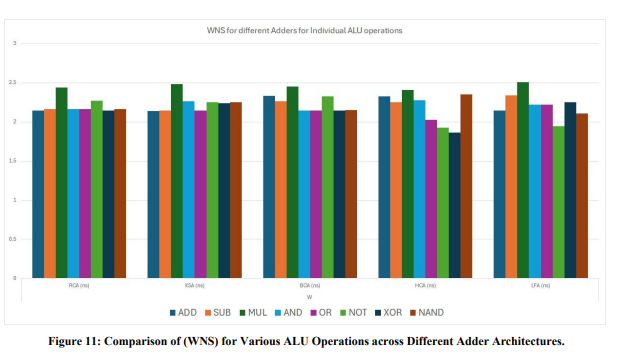

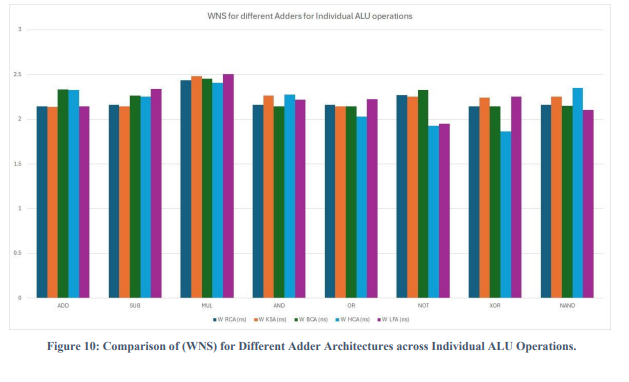

- Performed performance analysis comparing conventional arithmetic units with the proposed design.

- Achieved improved computation speed, hardware efficiency, and processor throughput, making it suitable for high-performance embedded systems.